1 引言

CAN(Controllcr Arca Nctwork)是由ISO(International Organization for Standardization)定义的一种串行通信总线,它是一种能有效支持高安全等级的分布实时控制的网络通信协议,属于现场总线通信的范畴[1]。CAN总线具有多主、优先级仲裁、短帧结构的优点,且有错误检测、错误限制和错误处理的能力,CAN总线网络已被广泛应用于各种工业通信环境中[2]。SJA1000是一种独立的CAN 控制器,用于移动目标和工业区域网络控制;它是PHILIPS半导体PCA82C200 CAN 控制器BasicCAN 的替代产品,新增加了PeliCAN工作模式,这种模式支持具有多种新特性的CAN 2.0B 协议[3]。

采用FPGA+SJA1000架构的CAN总线控制器接口设计是目前应用最为普遍和流行的,在大部分区域网络传输信息的控制现场发挥着重要作用[4]。CAN总线通信的架构方式有很多种,如利用DSP或者ARM的片内外设Ecan内核架构的CAN总线通信,以及本文有论述的FPGA+SJA1000的CAN总线通信架构方式等。由于DSP、ARM的片内外设Ecan内核架构的CAN总线通信采用邮箱的配置方式实现通信,相较于FPGA+SJA1000的架构方式比较复杂,不利于工程应用。本文采用FPGA+SJA1000的架构方式,结合控制系统与引信数据装定的通信协议,实现基于CAN总线通信的数据装定和数据应答处理。

2 系统概况

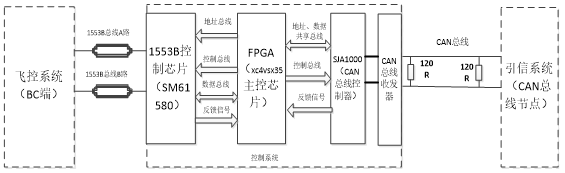

某型号控制系统通过CAN总线实现与引信数据装定,将定时参数、计数参数等参数发送至引信,实现引信内部延时等功能。在控制系统数据装定架构中,飞控系统通过1553B总线向控制系统发送CAN总线通信的指令数据,经控制系统FPGA解析处理后,获取到引信数据装定指令;FPGA控制SJA1000控制器将引信数据装定指令通过CAN总线发送至引信;引信获取装定数据后,对数据进行解析,并向控制系统应答装定结果,最终实现引信数据的装定和应答处理。本系统采用FPGA+SJA1000的方式实现CAN总线的通信,在控制系统和引信通信的两个节点之间并联120Ω电阻,可有效防止信号反射,提高信号传输的稳定性和可靠性。某型号控制系统CAN总线通信系统架构如图1所示。

图1 CAN总线通信引信数据装定架构图

3 硬件架构

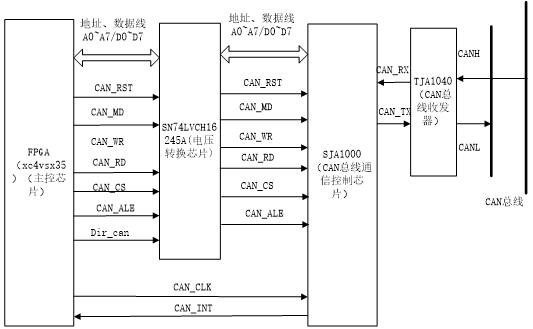

该系统FPGA主控芯片采用Xilinx公司V4系列的Xc4vsx35芯片作为核心控制器。该器件具有逻辑单元24192个、Slice区15360个、Block RAM 162 KB,用户I/O数448个,满足控制系统对SJA1000通信总线控制要求。架构中采用独立控制器SJA1000作为CAN通信总线的控制器。由于SJA1000与FPGA之间信号的电平不一致,因此,在SJA1000与FPGA间增加SN74LVCS164245进行信号之间电平转换处理,将两者之间3.3V的信号转换为5V的信号。当FPGA输出对SJA1000的控制信号、地址和数据后,SJA1000输出数据波特信号,并通过CAN总线收发器将信号发送至CAN总线上。本文设计的重点就是把SJA1000中的寄存器地址数据写入到SJA1000中,并配合地址锁存信号ALE、写允许信号WR完成对SJAl000特定的命令字写入寄存器中,从而实现对SJA1000工作模式、中断设置等工作状态的配置。在SJA1000工作状态确定后,FPGA即可实现对其数据写入和读出的操作,从而实现CAN总线通信控制。CAN总线通信硬件架构如图2所示。

图2 CAN总线通信硬件架构

4 软件架构及实现

4.1 软件架构及组成

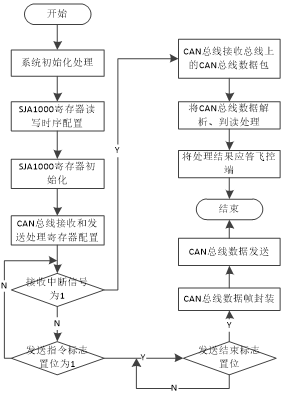

在CAN总线通信软件设计时,根据系统需求将软件进行初始化处理,通过对SJA1000控制器的寄存器的读写时序进行配置,实现对SJA1000寄存器的读写操作,并配置相应的值,从而实现SJA1000的初始化处理。在SJA1000寄存器初始化结束后,进行CAN总线通信控制,此时,FPGA控制软件对SJA1000控制器的中断信号进行检测,若接收到中断信号,则对CAN总线信号进行接收;否则对发送指令进行判读,若需要发送指令,则将CAN总线数据封装处理,并将数据发送至CAN总线的相应节点。FPGA+SJA1000实现CAN总线通信的软件架构如图3所示。

图3 CAN总线通信软件处理流程图

根据引信数据装定功能要求,结合FPGA+SJA1000结构的CAN总线通信的特点,实现该功能的软件模块由SJA1000寄存器读写模块、初始化处理模块、CAN总线收发处理模块、引信自检通信控制模块、引信数据装定及应答模块、引信CAN总线关闭控制模块等组成。

4.2 软件实现

4.2.1 SJA1000寄存器读写配置

SJA1000控制寄存器的内部寄存器对FPGA 来说是以外部寄存器形式存在而作为片内内存使用,因为 CAN 控制器可以工作于不同模式,所以须对模式信号进行相应的配置,模式寄存器的内容用来改变 CAN 控制器的行为,FPGA把控制寄存器作为读/写寄存器,通过设置模式位的值来实现数据对SJA1000的模式控制,其设置如下:

assign can_md = 1'b1;//1=Intel模式 0=Motorola模式

assign can_clk = clk_16M;//输入时钟

assign can_rst = rst;//复位信号

在SJA1000寄存器读写控制中,首先需要判读读使能还是写使能,从而进行相应的操作。读使能时,需要将CAN总线地址赋值到数据接口上,并将ALE地址使能信号置为1,完成地址数据的写入操作,在地址信号写入后,通过将读使能信号和片选信号输出,则可读出对应地址上的SJA1000寄存器内的数据。写使能时,则通过将CAN地址写入寄存器内,并将需要写入的数据赋值到数据接口,最后将写使能信号和片选信号输出,则可实现向SJA1000寄存器内写入数据。

4.2.2 软件初始化处理

在SJA1000控制的CAN总线通信初始化配置中,最主要的软件配置就是验收屏蔽寄存器的配置,而验收屏蔽寄存器的配置就是为了SJA1000的验收滤波器的滤波功能的实现,SJA1000 验收滤波器由4个验收码寄存器 ACR0、ACR1、ACR2、ACR3和4个验收屏蔽寄存器AMR0、AMR1、AMR2、AMR3 组成,这8个寄存器在 SJA1000 的复位模式下可由主控制器设置,通过对这些寄存器的设置可对接收信息构成非常灵活的滤波。

4.2.3 CAN总线收发处理

在进行CAN总线通信时,FPGA需要实时监测中断寄存器(IR)的值,若接收的中断寄存器标志置位,则进入接收数据的操作。FPGA可以通过向数据接口写入地址数据,并依次读取该地址对应的数据,直到数据读取结束。若需要发送数据,则发送数据标志为置位,则FPGA需要读取命令寄存器(CMR),并解析命令寄存器,查看CAN总线是否处于发送状态;若处于发送状态,则处于等待状态,直到发送结束标志置位;在发送结束标志置位时,FPGA将需要发送的数据根据CAN总线数据帧的格式进行数据帧封装,并启动发送数据桢的标志位,将数据帧发送到相应的节点。在发送数据时,同时需要写入发送缓冲区的标识符,这个标识符对于接收节点的滤波寄存器的匹配接收数据是非常有用的,只有滤波寄存器的值与该标识符成相关性,才可能接收该数据。

4.2.4 CAN总线数据装定处理

CAN总线数据装定时,需向引信节点发送自检指令,FPGA控制软件根据自检指令经封装处理后,启动CAN总线发送模块将自检指令发送至引信节点,当引信对自检数据进行处理后,进行自检处理,并将自检结果通过CAN总线接口应答。FPGA通过读取CAN总线中断寄存器标志位,确定读取自检应答数据的时机,若自检应答结果正常,则可进行数据装定处理,否则自检失败,退出数据装定。在自检成功后,FPGA根据数据装定协议进行封装处理,并启动CAN总线发送模块将数据发送数据,在获取装定应答结果,且应答结果正常后,则数据装定成功。在接收到CAN总线关闭指令后,通过发送关闭CAN总线指令,并接收到关闭指令应答结果后,将CAN总线挂起,使之处于待机状态。则CAN总线数据装定操作结束。

5 结束语

本文采用FPGA+SJA1000(CAN总线控制器)的架构方式,通过对硬件架构、软件架构、寄存器读写配置、软件初始化、CAN总线收发及数据装定进行设计,采用FPGA底层逻辑语言Verilog编写CAN总线通信时序,并通过主控端接收的引信数据装定指令,实现了对引信系统的数据装定及应答。深入研究了基于FPGA + SJA1000架构的CAN通信数据装定方案,为基于CAN总线的引信数据装定提出了相应的参考方法,可为CAN通信系统产品研发提供借鉴。

参考文献

[1] 王校伟.基于DSP和FPGA的CAN总线通信系统设计与实现[J].电子设计工程,2018,26(21):67-70+76.

[2] 吴坎,赵薇,李封.基于SJA1000和PCA82C250的CAN总线接口设计[J].机械设计与制造,2010(07):55-57.

[3] https://jingyan.baidu.com/article/7e4409533cb30e2fc0e2efa5.html

[4] 张鹏.一种基于FPGA的高速串行通信总线的设计与实现[J].电子质量,2021(08):19-22.