一、集成电路检测常识

对相关的集成电路进行检测之前,首先要对其内部构造完全熟知,充分了解其电路走向、功能和参数要求,还要了解其引线引脚分布走向、各引脚波形状况及电路工作原理。测试中要避免引脚间短路。在对集成电路进行带电测量或用示波器进行波形测试的过程中,必须绝对避免短路问题,规范的方式是在同引脚直接连接的外围电路上进行测量。测试中必须保证焊点牢固,避免虚焊。焊接过程必须要快速准确,一定要选取正规内热式烙铁。焊接完成之后,不要马上通电测试,要先确保焊接牢固并且没有短路,之后才能进行通电测试。严格禁止在无隔离变压器的情况下用已接地的设备进行测试。由于测试前对电气设备的电源性质可能并不了解,误操作可能造成电源短路并波及集成电路,进而导致器件损坏。注意电烙铁的绝缘操作。进行焊接时不能带电作业,这是因为不能保证电烙铁的绝缘性符合标准。特别是针对 MOS 电路进行焊接过程,更要注意操作的严谨。慎重对集成电路的损坏形成结论。因为集成电路在普遍情况下都是直接耦合的,如果之间的单个电路状态有所变化,会直接导致测试结果的变动,并不一定是集成电路已经损坏。

注意集成电路的散热情况。由于大功率集成电路附带散热器,工作时会有大量的热量放出,散热不佳极易引发集成电路的毁坏。选用内阻相对大的测试仪表。为避免测试误差,通常在选择测量集成电路引脚直流电压的仪表时,都会使用内阻在 20KΩ/V 以上的仪器。

二、集成电路失效形式及失效分析流程

1.物理失效形式

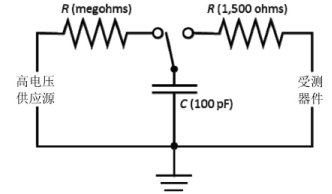

集成电路的物理失效形式基本分为两种,ESD静电放电模式和 LATCH-UP 损伤模式。对于 ESD 静电放电模型,一般可划分为三种:HBM 人体放电模型 (human baby model)、MM 机器放电模型(Machine Model)、CDM 充电器件模型(Charged-device Model)。人体放电模型是模拟人体静电放电对电子器件的作用。其等效电路如图 1 所示,其中 R(1500Ω)为等效人体电阻,C(100p F)为等效人体电容。

图 1 人体放电模型等效电路图

图 1 人体放电模型等效电路图

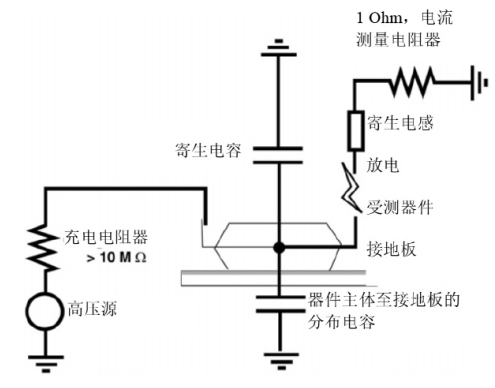

CDM 充电器件模型是已带电的器件通过管脚与地接触时,发生对地放电引起器件失效。其典型模型如图 2 所示。

图 2 典型充电器件模型

图 2 典型充电器件模型

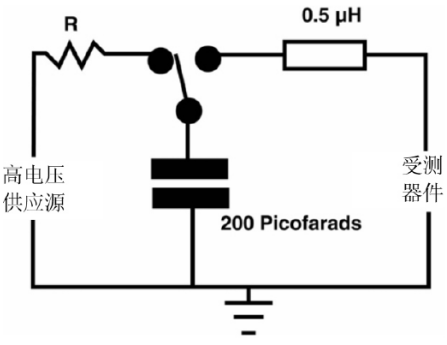

图 3 典型机器模型电路

图 3 典型机器模型电路

MM 机器模型是模拟带电机器对电子器件放电造成的损伤。典型机器模型电路如图 3 所示。与HBM 人体放电模型相比,机器模型没有电阻,电容则相对要大。对于全部的集成电路失效而言,ESD 静电放电模式和 LATCH-UP 损伤模式所占比例已经超出了百分之八十。所以集成电路抗闩锁 LATCH-UP 损伤的能力和在 ESD 静电放电等级方面的评判,已经成为集成电路整体可靠性方面的关键评价标准。

2.失效分析过程

集成电路失效分析通常分为四步流程。首先是无损失效分析。是指在不损坏样品的情形下,对于样品失效情况做出评判。常用的无损失效分析手段包括:①外观分析,即人眼进行观测,直接鉴别电路的外观有没有明显损伤和缺损;② X 射线分析,即借助 X 射线对于样品进行透视检测,通常使用这种方式检测集成电路引线的问题;③ 扫描声学显微镜检测,即借助超声波对样品进行检测,可检测器件内部问题,这种检测方式主要针对集成电路塑封条件中的水汽或高温导致的相关问题。针对已经失效的集成电路,采取开封镜检。对于不同的集成电路及封装方式,开封镜检需采用对应的不同处理方式。当前有三种处理方式:(1)全剥离法。即将集成电路的外路彻底去除,仅保留内部完整芯片,进行内部电路的观测。这个方式的缺陷就是内部电路的引线都被损坏,不能进行通电测试。2)局部去除法。即借助研磨机,对芯片覆盖的树脂采取研磨操作。这种方式的优势是开封环节没有对芯片内的电路以及引线形成破坏,在开封之后仍可进行通电测试。3)全自动法,这个方式就是使用硫酸喷射的方式,对于计划去除的区域进行开封处理。对失效电路展开电性分析。电性分析技术通常划分为三个方面,即缺陷定位、电路分析法及微探针检测分析。(1) 缺陷定位,这项技术就是对于缺陷的具体定位方式,具体技术有:OBIRCH 技术、Emission显微镜技术以及液晶热点检测技术等。(2) 电路分析法。即对照集成电路的原理图及芯片电路图纸,对失效集成电路进行渐进检测,逐步减小检查范围,并结合微探针检测技术,进行失效定位。(3)微探针检测技术。该技术通常是结合电路分析法进行,使用微探针对于内部器件的相对数值做出检测。最后进行的步骤是针对失效集成电路进行物理分析。物理分析的方式主要有四种。第一、聚焦离子束(FIB)方式,其目的是对集成电路样品形成剖面以便观察,相比传统的手工研磨法,借助聚焦离子束切削能够做到精准的操作,获取更高的准确率。第二、扫描电子显微镜(SEM),目的是对于最终集成电路样品成像并进行研究。第三、透射电子显微镜(TEM),对比扫描电子显微镜,其分辨率能够达到 0.1nm 的层级,能够对集成电路的问题做出更清晰的反馈,可以进行问题的深入探究。面对缺陷排查问题,可以行成更为精准的操作。第四、VC 定位技术(Voltage Contrast)。这个技术是 SEM 或 FIB 在进行了升级之后形成的全新技术,它使得集成电路失效问题的确定环节更为快速精准,可以对缺陷问题精准定位。该技术的原理是,在电路板的表面,借助 SEM 电子束或者 FIB离子束的使用,获取差异位置的具体电势,并在屏幕上以差异亮度进行显示,通过对于不同亮度的对照,寻找异常亮点,从而确认失效点的具体位置。采用上述四种方法,可基本满足集成电路失效分析的需求,实现问题的准确分析与定位。

结束语

综上所述,在现代化社会的发展中,集成电路技术被广泛地应用,加大对其的研究,提升整体的技术水平,以便尽快实现对失效产品的精确分析与定位,能够基本满足现阶段集成电路失效分析的各类需求。

参考文献:

[1] 赵国芳,刘晓明.基于Proteus的集成电路应用课程教学案例设计[J].电子技术与软件工程,2019.05:257-258.

[2] 张建国,李路量.关于人工智能发展趋势的一些思考及建议[J].网络安全技术与应用,2019(12):247-248.

[3] 王晓路.我国各省市集成电路产业政策情况分析与有关建议[J].处理机,2019.3:1-6.