1 FPGA 软件测试原理

当前 FPGA 软件测评流程主要包括: 静态检查规则、跨时钟域检查、功能仿真、门级仿真、逻辑等效性验证、动态时序仿真、静态时序分析、实物验证。其中,软件仿真借助仿真软件编写测试激励 Testbench 模拟信号输入,同时采集被测软件输出信号 VCD 波形,进行结论判定。实物验证需要搭建芯片真实运行环境,与外围电路、设备一同运行,通过功能表现验证软件正确性。软件仿真和实物验证在一定程度上互为补充,是当前 FPGA 软件测评主要验证手段。但随着装备软件应用范围及应用场景的不断变化,当前验证手段已不能满足对 FPGA 软件测评越来越高的要求。

2 VCD波形的FPGA实物自动化测试技术

2.1 VCD 波形分解压缩技术

通过对 VCD 波形文件内部的变量进行提取,生成单变量的 dat 数据文件。dat 文件是单引脚波形变化信息,在生成过程中,只需对引脚信号的变化时刻和对应值进行记录,从而实现信号的压缩。波形压缩转换技术使母板上的 FPGA 能够通过硬件电路对信号进行完整的复原,并且避免了每一时刻都需要对所有信号进行记录的状况,使系统的整体性能得到提高,确保了信号能够被以全速率进行发送和采集。这种技术也巧妙地避开了数据存储和传输的性能瓶颈,使系统能够以线速生成激励、采集响应。对于存在多个时钟域的待测对象,按时钟域将接口信号划分为相互独立的若干组,每组接口信号均包含 inout、input 和 output 信号。对于验证平台,同样以时钟域将 Test pattern 划分为若干组,每组 pattern 对应时钟域接口信号的驱动。时钟域的划分方法如下:a) 根 据 时钟域 pattern 被划分为若干个子pattern,例如 pattern _1、pattern _2、pattern _3、pattern _4,每个 pattern 对应一组测试接口信号,子 pattern 之间相互独立,每个子 pattern 具有完整的帧结构;b) 根据时钟域将 pattern 加载、存储,划分为不同组,例如 group1、group2、group3、group4;c) 每个 group 均包含若干个 PIN_INOUT、PIN_DRIVE 和 PIN_CAPTURE 信号;d) CLK 模块提供多个时钟,例如 clk1、clk2、clk3、clk4;e) 根据每个 group 中信号的时钟,配置寄存器中group 的时钟,例如,如果 group 信号处于不同时钟域,可以 group1 选 clk1,group2 选 clk2,group3 选 clk3,group4 选 clk4; 如果某两个或多个 group 处于同一时钟域,可以是 group1 /2 都选 clk1,group3/4 选 clk2,等等。

2.2 测试向量生成技术

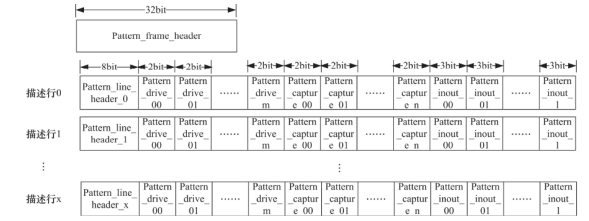

测试向量由 VCD 波形文件转化得到,软件将测试向量发送到验证平台,验证平台将其转化为激励向量,实现输入文件到测试激励的转化。首先定义报文,报文根据输入文件的信息结构特征和验证平台的工作原理进行设计。报文定义如图 1所示。

图 1测试向量报文

a) 将测试向量定义为帧结构,由帧头和若干条描述行组成;b) Pattern_frame_header[31: 0]: 定义测试向量的基本信息,包括描述行总数目、测试向量的归属时钟域等;c) Pattern_line_header[7: 0]: 定义描述行的基本信号,包括保持周期数等,对于有判断期望值的行保持周期数必须为 1;d) Pattern_drive[1: 0]: 定义 PIN_DRIVE 信号的驱动值,00 保持原值,01 驱动为高阻,10 驱动为低电平,11 驱动为高电平;e) Pattern_capture[1: 0]: 定义 PIN_CAPTURE 信号的期望值判断,00: 不关心,01: 不关心,10: 判断并且期望值为低电平,11: 判断并且期望值为高电平;f) Pattern_inout[2: 0]: 定义 PIN_INOUT 信号为驱动或期望值,Pattern_inout[2]为方向位,0: 驱动信号,1: 期望值判断; Pattern_inout[1: 0]定义与 Pattern_drive[1: 0]一致。

2.3 测试激励注入技术

测试向量文件采用 FPGA 片上的 block RAM 搭建双端口 DPRAM 组来存储,DPRAM 一端处于 PCI-E_slave 用户接口时钟域,接受来自 pattern_load_ctrl 写入的数据; 另一端处于 PIN 的时钟域,读出数据给 pin_ctrl,用于控制 PIN 的驱动和获取,将测试向量映射到对应引脚,完成测试激励注入。

3 实验验证

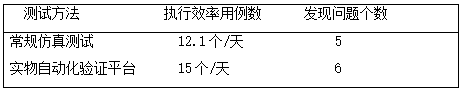

实物自动化验证平台包含子板和母板,外部连接辅助计算机。首先通过 PCI-E 接口接收 VCD 波形文件,验证平台将其压缩转换为测试向量。然后,向测试向量文件中 mem[2]、mem[3]注入错误行,通过验证平台将测试向量加载到被测 FPGA芯片。随后验证平台读取从被测 FPGA 上返回的输出数据,经过与期望值比较,得到验证报告,结果显示在列表中。点击结果列表,可显示验证平台波形,通过与注入错误行前的原始波形比较,可定位问题。注入错误行前原始波形和注入错误行后波形。注入错误行前,波形图中 cap_error_valid 信号一直为低电平,实测结果与期望一致。测试向量注入错误行后,cap_error_valid 信号出现两处高电平,导致两处错误,两处错误的期望值分别为 0x00、0x03,真实值分别为 0x02、0x01。借助自动化验证平台进行某型星敏感器 FPGA 软件测试,通过仿真建模和编写测试激励实现常规仿真测试,生成的 VCD 文件进行实物自动化验证。二者进行比较发现,实物自动化验证平台工作效率显著提高,发现了常规 FPGA 仿真测试 未发现的问题,如表 1所示。

表 1 测试结果对比 实验验证了实物自动化验证平台可 正确转换VCD 波形,并将转换后的测试向量加载至被测器件。通过读取返回值,与期望值比较后生成测试报告,并可对问题进行追踪。实验结果表明,该平台能够正确施加测试激励,有效检验出被测器件的错误,具有验证过程简单、验证速度较快等优点。

实验验证了实物自动化验证平台可 正确转换VCD 波形,并将转换后的测试向量加载至被测器件。通过读取返回值,与期望值比较后生成测试报告,并可对问题进行追踪。实验结果表明,该平台能够正确施加测试激励,有效检验出被测器件的错误,具有验证过程简单、验证速度较快等优点。

结束语

综上所述,本文提出一种基于 VCD 波形的 FPGA 实物自动化验证技术,用以解决仿真测试和实物测试的弊端。实物自动化验证技术突破了数据传输瓶颈,保证了数据实时性,提高了测评效率,同时 VCD 信号的灵活性保证了测试充分性。该技术可作为当前 FPGA 软件测试的有力补充,并将在未来的 FPGA 软件测试中发挥重要作用。

参考文献:

[1] 齐宣,李一民,龙华,等.基于 TCP/IP 协议栈的串口-网口通信方案设计[J].电子测量技术,2018,41(08):123-127.

[2] 王为民,刘刚.关于FPGA实物自动化测试技术探究[J].电力工程技术与设计,2021,(01):133-135.

[3] 刘玉明.基于VCD波形的FPGA实物自动化测试技术[J].工程技术,2020,(02):155-156.